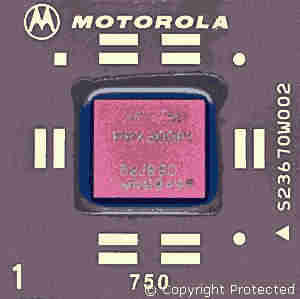

Motorola PowerPC 750 / RAD750

The Motorola PowerPC 750 architecture came from the IBM POWER architecture as shown in the RAD6000 article. This was one of the first implementations of reduced instruction set computing (RISC) architecture consisting of 6.4 million transistors. The PowerPC also has a single event upset (SEU) tolerant version called RAD750, which has approximately 10.4 million transistors.

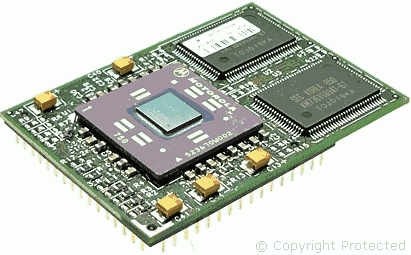

L2 Cache Memory

In this photograph, you can see the external L2 cache memory chips, which was available in options of 256 K, 512 K, and 1 MB. The RAD750 did not have the L2 cache, as it would require SEU tolerance, which would increase the final cost.

Die Size

The RAD750 had a bigger die size of 130 mm × 130 mm and came in a 360-pin column grid array (CGA) package, whilst the PowerPC came in a 255-pin ball grid array (BGA) package.

This Article Continues...

RAD750 ProcessorPowerPC 750 Processor

Mars Rover Curiosity

Single Board Computer (SBC)

RAD750 Processor Architecture

Radiation Hardened

Mars Rover Power Supply